The total number of memory accesses involved (inclusive of the OP code fetch), when an 8085 processor executes the instruction OUT 80H is

A 4-bit ripple counter and a 4-bit synchronous counter are made using flip-flops having a propagation delay of 10ns each. If the worst case delay in the ripple counter and the synchronous counter be R and S respectively then.

A 1ms pulse can be converted into a 10ms pulse by using which one of the following?

The number of unused states in a 4-bit Johnson Counter is

The highest speed counter is

Consider the following statements regarding registers and latches.

1.Registers are temporary storage devices, whereas latches are not

2.A latch employs cross-coupled feedback connections.

3.A register stores a binary word, where as a latch does not.

The correct statement is/are.

A Ring oscillator consisting of 5 inverters is running at a frequency of 10 MHz. The propagation delay per gate is :

A 5 bit module-32 ripple counter uses JK flip-flop if the propagation delay of each FF is 50ns, maximum clock frequency is (in mHz)

Match List-I (circuit) List-II (application) and select the correct answer using the code given below.

|

List-I |

List-II |

|

A. Ripple up counter |

1. Division. |

|

B. Synchronous down counter. |

2. Multiplication |

|

C. Shift left register |

3. To create delay. |

|

D. Shift right register. |

4. Transient states |

The counter which requires maximum number of flip-flops for a given MOD number is

A circuit consists of two synchronous clocked J-K flip-flop connected as follows: the circuit acts as a.

The initial state of MOD-16 down counter is 0110. After 37 clock pulses, the state of the counter will be.

If the memory chip size is 1024 × 4, the number of memory chips required to design 8 K memory is

If (11X1Y)8 = (12C9)16 then the value of X and Y are:-

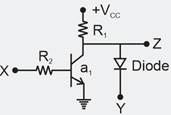

In the circuit shown Q, has negligible collection–to-emitter saturation voltage and the diode drops negligible voltage across it, under forward bias negligible voltage across it. If Vcc is 5v, X and Y are digital signals with 0v as logic 0 and Vcc as logic 1. The Boolean expression for Z is

When the Boolean function

)

is minimized what does one get?

The minimum number of comparators required to build an 8-bit flash ADc is.

Assertion (A): the switching speed of ECL gate is very high.

Reason (R) : the devices in ECL gate operate in active region .

Which of the following circuits come under the class of combinational logic circuits?

1. Full adder 2.Full subtractor 3.Half adder 4.JK flip-flop 5.Counter

Select the correct answer from the codes given below.

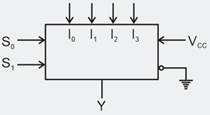

Find ‘Y’ from the given MUX when

& selection lines S0,S1 can be the choice of user to use only binary singles.